Paso 2: Crear el Banco de pruebas y simular el circuito

Como el propósito de este banco de prueba es demostrar el error, en lugar de simular todas las posibles transiciones de entrada, Disenaremos una secuencia de entrada que puede provocar la falla en la salida del circuito. Observando el circuito, hay una trayectoria desequilibrada entre la entrada B y salida X (es decir, hay dos caminos para propagar los cambios de B a la salida con diferentes retardos). Así que la falla ocurre cuando A y C son constantes y B cambia. Aquí está la descripción que vamos a crear en el bloque inicial de Verilog de banco de pruebas:

1 entero k = 0;

2

3 inicial comienzan

4 / / inicializar entradas

5 = 0;

6 = 0;

7 C = 0;

8

9 / / esperar 100 ns para el reajuste global a fin

10 / / añadir estímulo aquí

11

12 para (k = 0; k < 4; k = k + 1)

13 comienzan

14 {a, C} = k;

15 # 5 = 1;

16 # 5 = 0;

17 #5;

18 final

final 19

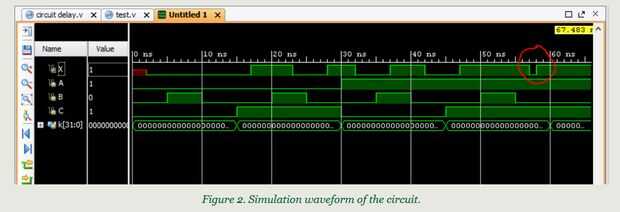

Simular el Banco de pruebas en el simulador de Vivado, y obtendrá la pantalla de forma de onda, como se muestra en la figura 2 anterior. El círculo rojo en la forma de onda especifica la falla. Por lo que la falla ocurre realmente cuando A es 1, es 1 y B cambia de 1 a 0. La duración de la falla es de 1ns.