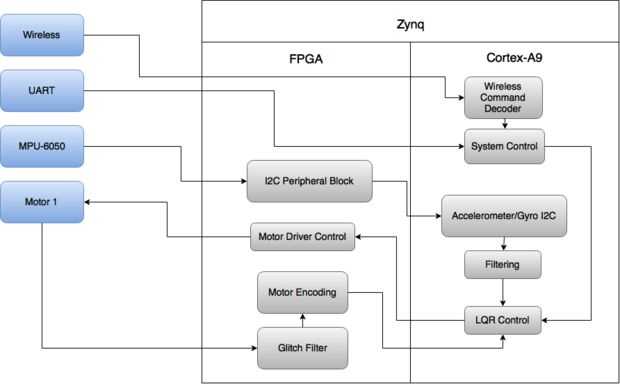

Paso 3: FPGA tela

El código fue dividido entre la tela de la FPGA y el ARM Cortex-A9 CPU en el chip Zynq. La tela FPGA fue encargado de hacer salir una onda PWM al motor, así como filtrar y lectura de la velocidad del motor.

Control de conductor del motor

El conductor del motor utilizado determina la velocidad de salida por lectura en el ciclo de trabajo de una forma de onda PWM de 500 Hz de la placa de Zynq. Esta generación de PWM se realizó en hardware. Este bloque llevaría en un valor de ciclo de deber entre 0-100 y la salida PWM del regulador del motor. El efecto neto de esto era que todo el CPU tenía que hacer para configurar la velocidad del motor escribir un valor entre 1 y 100 en un registro. El motor entonces se gira a una velocidad predecible.

Filtro de interferencia

Mientras que nuestro método de codificación óptica para detección de velocidad funcionaba bien, la entrada era ruidosa a veces. La solución a este ruido era un filtro de interferencia simples. El bloque lee en el codificador óptico y si las 5 últimas lecturas eran altas, emitiría un alto valor. De lo contrario emitiría un valor bajo. Esto debounced la señal ruidosa el codificador óptico y hecho apto para la medición.

Codificador de motor

Este bloque en la entrada del codificador filtrada y genera un valor de velocidad de la CPU. Trabajó por cuenta de las señales de reloj de un reloj de 100 MHz entre cada flanco ascendente del entrada de encoder. Tomando un promedio de 16 de estos valores, hemos sido capaces de obtener una velocidad en garrapatas/pieza de cinta. Entonces, sabiendo que había 8 trozos de cinta en el volante, fueron capaces de convertir este valor en ticks/revolución. Este es el valor que finalmente se pasó a la CPU. Lo importante de este valor es que a medida que aumenta la velocidad de rotación, el valor de "velocidad" disminuye. Aunque hubiéramos preferido pasar un valor de velocidad de rotaciones por segundo, tendríamos que tomar una inversa, que es muy costosa en una FPGA.