Paso 6: Salida - CDMA y el bloque diseñan parte 1

El propósito del es el controlador HDMI para visualizar las imágenes procesadas. Ahora, con el controlador implementado y listo para ir debemos pensar acerca de este controlador de alimentación con datos. Dado que mucho del proceso de mejora de imagen llevará a cabo en el PS (sistema de procesamiento = procesador ARM) y las imágenes resultaron voluntad reside en la RAM de DDR. Así que tenemos una manera de obtener los datos desde la RAM al controlador HDMI.

Hay realmente varias formas válidas para conseguirlo. Podríamos usar:

-VDMA IP con una corriente de AXI para vídeo IP

-IP DMA con AXI STREAM de vídeo IP

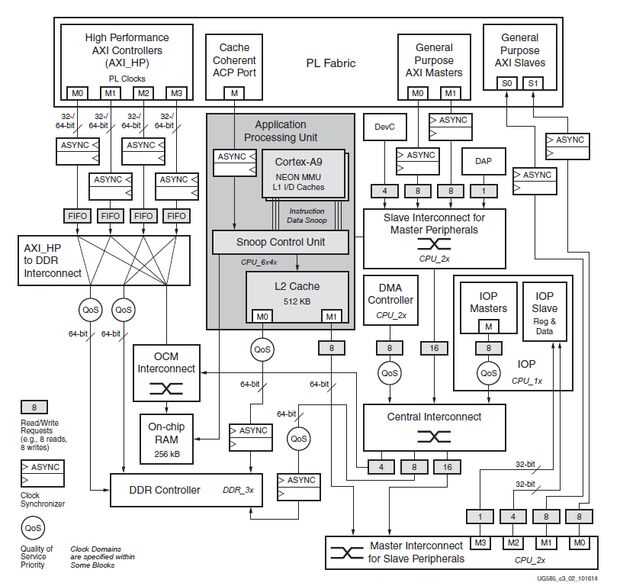

-El DMA en el PS (visible en el esquema anterior)

-IP CDMA

Las dos primeras opciones son ambas buenas opciones pero tienden a utilizar más recursos en la FPGA. La tercera se sufre cuando se trata de rendimiento porque sólo puede utilizar los puertos de GP y no los caballos de fuerza más. El cuarto es nuestra elección para este proyecto. El CDMA tiene una impresión del pie del menor en la utilización de lógica de la FPGA y puede utilizar los puertos de HP.