Paso 7: Salida - CDMA y el bloque diseñan parte 2

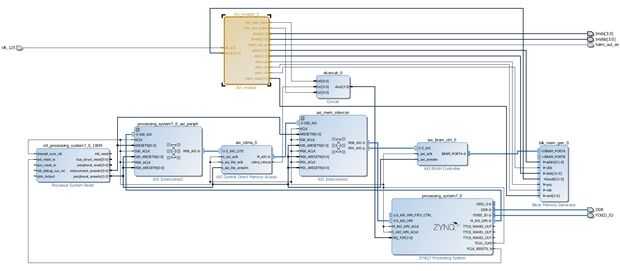

Por lo tanto, nuestro plan es programa el CDMA de la PS vía un interfaz AXI LITE para leer 4 filas de la imagen de la DDR RAM a través del puerto HP0 y escribir ellos a BRAM en el PL usando un AXI BRAM controlador IP (esta IP se utiliza para traducir entre la interfaz amo AXI de la CDMA y la interfaz de BRAM). Una vez que las filas en la BRAM pueden ser fácilmente rojo por nuestro controlador HDMI y pantalla. El problema es que debemos proporcionar la CPU con una interrupción después de que hemos terminado estas 4 filas para reprogramar el CDMA para transferir las filas siguientes. También tenemos que proporcionar una interrupción adicional para el final de la imagen para que la imagen está alineada correctamente. Debemos agregar esta funcionalidad al controlador HDMI y paquete a una IP para facilitar su uso en nuestro diseño de bloque.

Las interrupciones generadas en nuestro controlador HDMI se conectarán a las interrupciones del IRQ_F2P compartida del PS (usted puede leer más acerca de interrupciones en el capítulo 7 de la Zynq Manual técnico de referencia aquí http://goo.gl/nEQrBv ).

También necesitamos aumentar la FCLK_CLK0. Este es el reloj para todos los AXI IP en el diseño de nuestro bloque. Este es el reloj que se utiliza para escribir en la BRAM así queremos que sea más rápido que el reloj que dice de él (el reloj de pixel = 148.5 Mhz). Vamos a aumentar la frecuencia a una segura 250Mhz.

Tenemos que calcular cuánto vamos a necesitar de BRAM. Habrá 4 filas en un momento en la BRAM así 4 filas * 1920 píxeles * 3 canales de color = 23040 Bytes. Entonces podemos utilizar el Editor de la dirección de Vivado para definir el tamaño BRAM a 32KB.

Con toda la configuración de hardware hecha procederemos a la parte de software