EE214

Proyecto 5: Multiplexor, decodificador, codificador y palanca de cambios

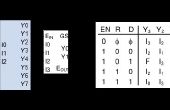

En este proyecto se diseño un multiplexor, un decodificador, codificador y una palanca de cambios usando Verilog HDL. En lugar de construir el circuito utilizando los operadores de la lógica, usted aprenderá a describir un circuito su comportamiento

Proyecto 2.1: Implementar un circuito de lógica Simple

En este proyecto, se descargar un archivo de bits a la placa para configurar la FPGA con cuatro diferentes circuitos de lógica. Los circuitos utilizan botones e interruptores para las entradas y LEDs para las salidas. Debe sondear los circuitos lógic

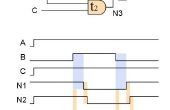

Proyecto 7: Simular falla y demora en circuitos combinacionales

En este proyecto, vamos a examinar el retardo en circuitos combinacionales. Vamos a decirle al simulador de la demora de cada puerta en Verilog y simular los circuitos para ver cómo retardo puede afectar el comportamiento de un circuito combinacional

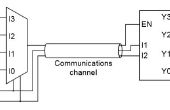

Proyecto 6: Un sistema de comunicación Simple

En este proyecto, se diseño un mux 4 a 1 y un decodificador con una señal de enable como un "mux de" implementar un transmisor de datos en serie simple. Mux y de mux se implementará en dos ficheros Verilog para su reutilización futura. Otro fich

Proyecto 3.1: Mayoría de 5

¿Cómo se podría encontrar una mayoría de los votos si cada uno de los cinco votantes tiene un interruptor para votar sí o no? La lógica es bastante simple y se utilizará en este proyecto. Cualquier momento hay tres o más de los cinco que voto Sí, ent