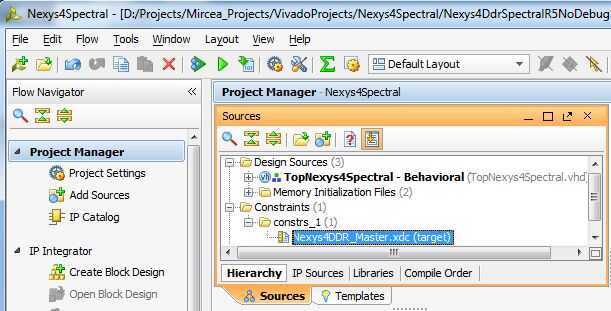

Paso 5: Volver a construir el proyecto Vivado. Comprender, editar y modificarlo.

En Nexys4DdrSpectralSources.zip, abra el archivo readme.txt que describe el procedimiento para construir el proyecto. Siga los pasos para volver a construir el proyecto Vivado de las fuentes siempre.

Nota importante: Como se muestra en el archivo readme.txt, el proyecto está listo para compilar para un tablero de Nexys4 DDR. Si desea compilar para un tablero de Nexys4, quite el proyecto limita el archivo llamado Nexys4DDR_Master.xdc y agregue en su lugar el archivo llamado Nexys4_Master.xdc. (\src\constraints).

Analizar la estructura del proyecto:

- TopNexys4Spectral - produce un pulso de flgStartAcquisition ciclo de cada 100ms, que inicia un cómputo. Crea una instancia de:

- clkGenInst - un generador de reloj de núcleo IP Vivado. Utiliza un reloj de 100MHz entrada y genera:

- Reloj de 25MHz para el controlador VGA

- 4,8 MHz para el componente de audio demo.

- Audio_demo_inst - el proyecto demo de Digilent Audio, como publicado y descrito aquí. Produce 48KSPS de señal de audio de 16 bits.

- Inst_fftBlock - calcula la FFT de la señal de salida de audio_demo.

- Crea una instancia de:

- TimeBlkMemForFft - core Vivado IP: 8 bits, 1024 muestras puerto dual RAM para almacenar la señal de audio y proporcionar a la base de la FFT.

- FftInst - core Vivado IP: calcula la FFT de la señal almacenada anteriormente.

- ResetStateMachine inicializa la base de la FFT.

- TimeCounter indexa las muestras en el TimeBlkMemForFft.

- TimeAcqSync sincroniza la TimeCounter con el flgStartAcquisition y el levantamiento de borde en el nivel cero de la señal de audio.

- FftLoadCounter indexa las muestras para cargar el core IP de FFT (muestras del tiempo).

- FftUnloadCounter indexa las muestras para descargar el core IP de FFT (muestras de dominio de frecuencia).

- Crea una instancia de:

- Inst_VgaCtrl, genera las señales de sincronización VGA, así como los contadores verticales y horizontales para localizar el píxel de muestra actual.

- Inst_ImgCtrl-genera la imagen de la pantalla VGA.

- Crea una instancia de:

- TimeBlkMemForDisplay - core Vivado IP: 8 bits, 1024 muestras puerto dual RAM para almacenar la señal de audio y proporcionar a la pantalla VGA. Copia sincronizada de TimeBlkMemForFft.

- FreqBlkMemForDisplay - core Vivado IP: 8 bits, 1024 muestras puerto dual RAM, para conservar muestras de dominio de frecuencia de audio y proporcionar a la pantalla VGA.

- Crea una instancia de:

- inst_LedStringCtrl – construye la imagen a mostrar en la tira de LED.

- Genera las definiciones de color del arco iris.

- Almacena los valores de las primeras muestras de dominio 30 frecuencia.

- Combina los dos info arriba para generar la demostración dinámica de frecuencia sobre los LED.

- Lee interruptores para seleccionar imagen estática o dinámica en los LEDs.

- Crea una instancia de:

- U1 - led_controller = controlador de led

- Obtiene datos de color para cada LED en la tira.

- Combina los tres colores para cada LED

- Combina la información de colores de LED 30 en una cadena de bits individuales.

- Codifica la cadena de bits como un código NRZ para conducir la tira de LED.

- U1 - led_controller = controlador de led

- clkGenInst - un generador de reloj de núcleo IP Vivado. Utiliza un reloj de 100MHz entrada y genera:

Modificar el proyecto sobre su conveniencia. No dude en utilizar todo o parte de él en sus proyectos.