Paso 4: Desarrollo de software

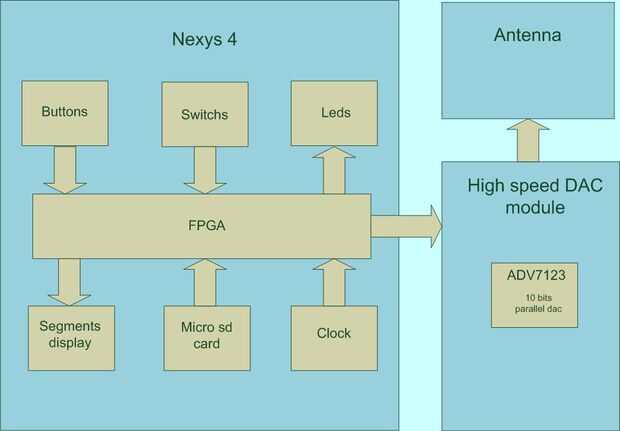

Para este proyecto usé lenguaje vhd y pocas cuadras de ip Xilinx.

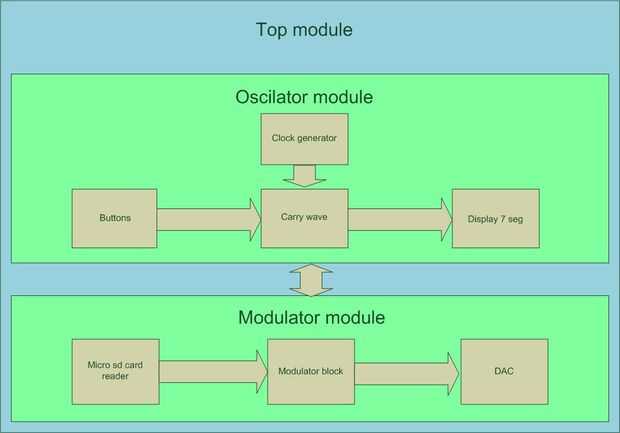

Este software dispone de dos módulos grandes.

Primer módulo se utiliza para generar una onda de frecuencia variable cosinus. Para este oscilador usé dds compiler 6.0 de Xilinx. Este bloque de ip tiene un montón de opción y todos son describe en documentación. El reloj de entrada para este módulo tiene 50 MHz y generar una onda de coseno de 10 bits con paso de 1 Hz. Esta parte está ya implementada y probada. Hasta ahora el CAD módulo y módulo del oscilador pueden generar correctamente las señales analógicas hasta 6 MHz (esta frecuencia es una limitación de hardware porque para primer módulo CAD usé una resistencia normal thd en salida de dac y después de 6 MHz aparece un montón de ruido).

Segundo módulo utiliza el cos onda y algunos datos binarios de la tarjeta micro sd para modular estos datos. Esta parte no está implementada todavía.