Paso 6: ¿Cómo el TWI transmitir datos?

Ahora nos gustaría discutir exactamente lo que está sucediendo cuando el TWI está transmitiendo datos.

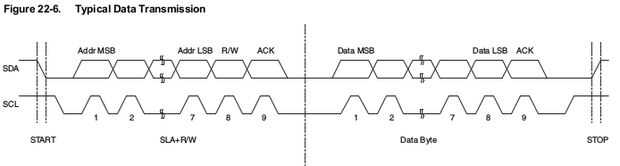

Lo primero que transmitimos es la "condición de inicio". Esto es una señal SDA cae cuando la señal SCL es alta. Así que si usted está buscando en las dos líneas se verá el SCL que va hacia arriba y hacia abajo entre 0V y 5V en una onda cuadrada 490 veces por segundo. La línea SDA, por el contrario, sólo se sienta allí en 5V. Ahora, de repente, la línea SDA cae a 0V al mismo tiempo que la línea SCL está en la parte alta (5V) de su ciclo. Esta es una condición de "start". Cuando el esclavo vea que pasar muelles en acción. Bien... Digo "resortes de acción" pero puesto que el esclavo frecuencia de la CPU es 16 MHz y la frecuencia SCL es 490 Hz significa que el esclavo tiene 32653 ciclos sentarse alrededor moviendo sus pulgares antes viene el siguiente ciclo SCL. Así es apenas "salto en la acción" pero obtienes mi significado.

Cuando el esclavo detecta una condición de inicio, las líneas de relojes y empieza a grabar el siguiente pulso de reloj alta. Los siguientes 7 bits será la dirección del esclavo que la maestra quiere hablar. Así, por ejemplo, supongamos que soy el esclavo y veo SDA a 0V la gota durante un pulso alto en la línea SCL. Entonces sé transmisión ha comenzado, entonces ver el SCL vaya a su parte baja y luego volver hasta alta otra vez, entonces miro SDA durante esta parte alta y es bajo (0V), esto significa que el primer bit de la dirección es 0, espere para el siguiente pulso alto y otra vez mira SDA, otra vez veo un 0V , por lo que el siguiente bit de dirección es otro 0, entonces el pulso siguiente veo 5V en la línea SDA, por lo que sé el siguiente bit de dirección es un 1, y esto continúa hasta que los bits de 7 dirección. Una vez que tengo la dirección de esclavo de todo 7 bit la comparo con mi propia dirección y si es diferente a ignorar la línea TWI después de eso. Si es la misma que mi dirección yo sé que el controlador maestro quiere hablar conmigo.

Espere para el siguiente pulso SCL alta y si el SDA es un 1 Entonces sé el maestro quiere leer de mí. Esto significa que el maestro está en "Modo de receptor de Master". De lo contrario si SDA fue un 0 en cambio significaría maestro quiere escribir a mí. Esto significa que el maestro está en "Modo de transmisor Master". Ahora sé que si yo soy el esclavo que dirección, y sé que si es una lectura o una escritura. Esto llevó a 8 ciclos de reloj y transmite 8 bits (7 bits de dirección y un poco de lectura y escritura) que es bueno porque estoy almacenar automáticamente ese byte en un registro de datos llamado TWDR que utilizo para averiguar si es mi dirección y si es una lectura o una escritura.

Entonces tengo que reconocer que he recibido que información para que tire de la línea SDA baja en el SCL alta próximo ciclo (el ciclo 9 desde el inicio) y esto le dice al maestro que tengo todo y estoy listo para el siguiente paquete de datos.

Si quiero, en este punto puedo tirar la línea SCL baja y sólo mantenerla allí como quiero. Esto será "pausa" cosas hasta dejarlo ir alto otra vez.

Una vez que las cosas siguen, supongo que fue una señal de escritura. Esto significa que el maestro ahora me envía algunos bytes de datos. Así que ver otra vez la línea SDA y recoger los bits vienen en. Esta vez habrá 8 bits (que de MSB LSB, es decir, de bit 7 para bit 0) y luego, si les tengo todo sin problemas, traerá la línea SDA a 0V en el 9 º ciclo reconocer que les tengo. Esto puede continuar indefinidamente, enviar byte tras byte. Cada vez que recibo uno será automáticamente almacenado en TWDR y es mi trabajo de copiar de allí y hacer algo con él antes de que el próximo byte de datos entra y escribe sobre él. Finalmente, cuando el maestro haya terminado me envío de datos, se enviará un estado de "parada". Esto es cuando el maestro tira la línea SDA alta en medio de la parte alta del ciclo de reloj SCL. Al ver esto he terminado con el TWI hasta detectar una condición de inicio seguida de mi dirección de nuevo.

Nota algo. Cuando el ciclo de reloj SCL está baja es cuando el controlador está estableciendo el bit siguiente. Por ejemplo, si quiero enviar un 1 al esclavo en el reloj siguiente ciclo, usar el tiempo cuando la línea SCL es baja entre los ciclos para establecer la línea SDA sea alta o baja para que cuando el próximo ciclo de alta aparece mi SDA línea ya está presentando la broca que quiero enviar. A continuación os dejo 0 o 1 toda fase alta hasta que el SCL se remonta hacia abajo y puedo ajustar otra vez a mi nuevo bit de datos. Por otro lado, si quiero enviar un comienzo o una parada, configurar un estado inicial en la parte baja del ciclo como de costumbre, pero luego en lugar de dejar simplemente que a través de la siguiente fase alta, la transición al estado opuesto durante la parte alta del ciclo.

Por ejemplo, decir soy maestro y he terminado de transmitir mi bytes de datos y quiero enviar una señal de parada al esclavo. Luego durante el próximo ciclo baja después he recibido la confirmación de mi último bit de datos voy a tirar la línea SDA baja y esperar, luego durante la siguiente fase alta de la SCL tirará la línea SDA alta. Esta transición le dice todo el mundo en la línea que se ha producido una condición de parada.

Debe examinar todos los diagramas en las páginas 208 a 211 y entender la mecánica de las señales de TWI. También discuten sobre "comienza repetida", arbitraje entre varios masters y otras cosas que no entrar ya que no necesitamos todavía.