Paso 2: Tipos de dispositivos de lógica programables parte II

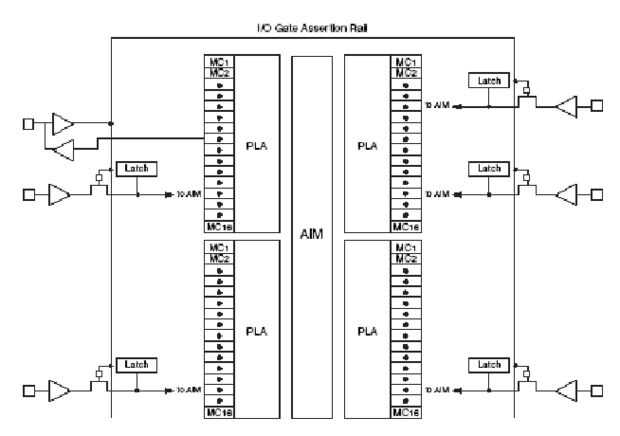

CPLDs por otra parte no necesitan un dispositivo separado para programarlos y no pierden su programa de energía es un ciclo o perdida. Su arquitectura es completamente diferente de la de un FPGA como se muestra a continuación. Además algunas CPLDs son capaces de manejar diferentes esquemas de señalización (LVDS, HSTL, etc.) así como tener la capacidad de consumir pequeñas cantidades de energía cuando está puesto en los modos de ahorro de energía.

Como se puede ver el dispositivo de Xilinx es explotado bloques de entrada-salida, matrices de lógica programable (PLA), y la avanzada interconexión matriz (AIM). Programación se hace vía los pines JTAG en el dispositivo.

�

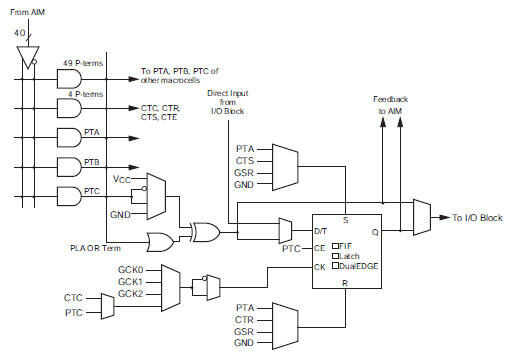

El PLA es parte del bloque de función. Como se puede ver las señales se enrutan de los bloques de la entrada-salida para el bloque de función y luego al objetivo y viceversa. En la foto puedes ver pequeños bloques etiquetados MC1 a MC16. Estas son las células de la macro.

Los dispositivos PAL, GAL y el PLD tienen una arquitectura que se muestra a continuación.