Paso 4:.. .adding un I2S convertidor...

Mirando la pajina otra vez noté que el I2S salida (realmente miro la documentación de chip usada en el proyecto de HifiBerry cuyo conductor estoy usando, el chip es un pcm5102) de la RPI es ligeramente diferente de lo que espera el chip oversampler. En general la señal de I2S "estándar" retrasa el una reloj de datos detrás de la señal LR. ¿Cómo compensar esto?

Hay dos maneras de abordarlo:

1. programa de un controlador de kernel que no retrasar los datos. El conductor de pcm5102 explícitamente establece la demora de datos 1 en el registro TXC_A del motor PCM SGCN (documentación aquí página 119 +). Cambiar esto a 0 debe hacerlo. Pero no me gusta compilar un Kernel de RPI ahora...

2. construir algunos vintage lógica para hacerlo, sí que es lo que me gusta :)

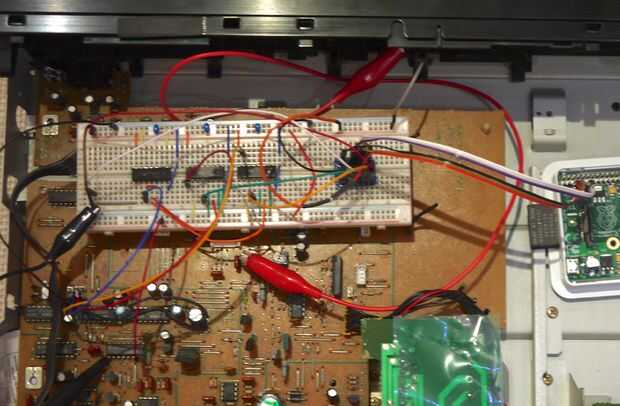

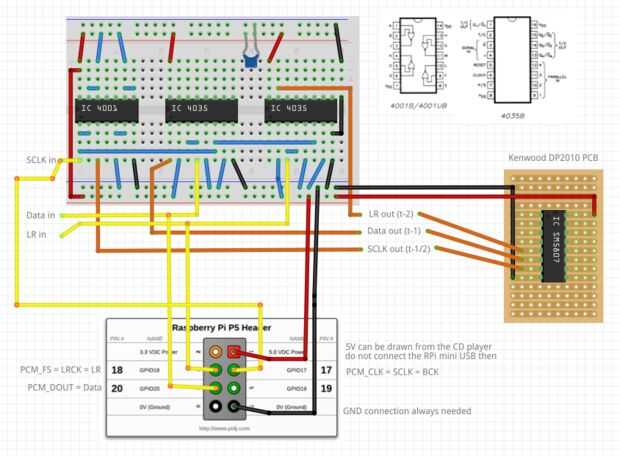

Aquí es un esquema...

La idea es retrasar los datos por el 1 y el LR de la señal por 2, esto mueve los datos hacia adelante en el tiempo (comparado con la señal LR) para que alinee como quería. Para ello, necesitamos 3 x D-chanclas y un inversor para el reloj. He encontrado 2 x 4035 y 4001 en mi colección vintage chip, estos (podría también será construir con 7474 74174 y algunos otros ICs).

El 4035 es un registro de cambio de 4 bits versátil (tiene 4 Flip-flop en una línea) 4001 es un x 4 ni que actúa como inversor entonces las entradas están apretados juntos.

Utilizo un 4035 a cambio de los datos y otra para cambiar de puesto el LR. Las salidas Q1-Q4 mostrará la entrada retrasada por 1-4 relojes (la entrada se desplaza a través del registro, que es que cambio los registros). Por lo que el oversampler recibe sus nuevos datos de Q1 de la palanca de cambios de datos y LR de Q2 de la palanca de cambios de LR. Simple ¿no? El oversampler obtiene el reloj invertido (especie de retrasado por ciclo de reloj 1/2) esto es necesario porque la palanca de cambios es necesario algún tiempo para reloj en los datos y ofrecer una salida estable.

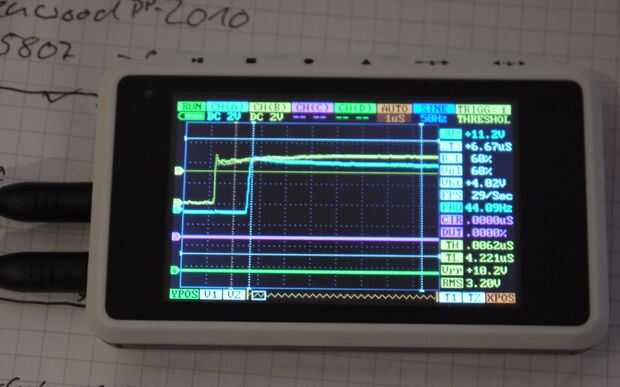

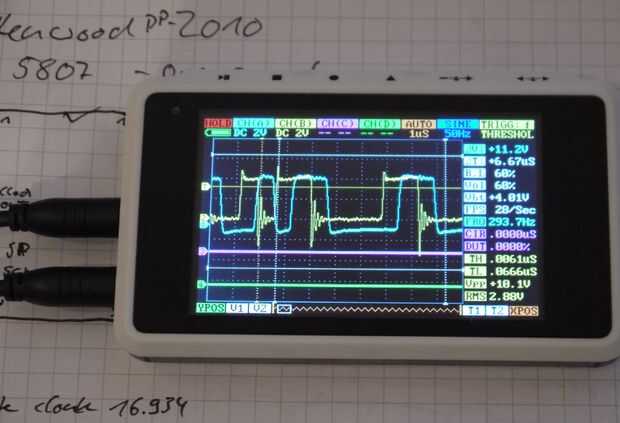

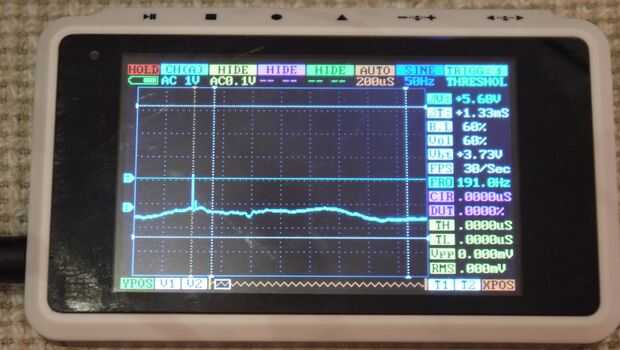

Las imágenes muestran la señal LR original y retardada, señal de reloj, análogo de salida con grietas.

Resultado...

Sí que suena como música.

Todavía un poco cracky (~ 50Hz tock tock) - podría ser una deriva del reloj, investigar más adelante...

¿Cómo suena?

Un poco ruidoso en los medios y altos - podría ser el auricular, la construcción de amplificador de auriculares es hasta un poco ruidosa para mi gusto y mis auriculares. Investigando...

Bajado el volumen de HP, mencioné que el PCB tiene un espacio para un pote de volumen. He insertado 4 resistencias que baje el volumen un poco.

¿Énfasis?

Que por sí solo es un hack de la vieja escuela, para superar limitaciones de 14 bits. Funciona un poco como el Dolby, supresión de ruido, cuando grabación añadir quitar ruido, cuando jugar y desaparezca el ruido de transmisión con él - algo como eso.

Corte del perno 36 de la TA9200 y conectados ahora abrir traza a un interruptor a tierra/5V por lo que yo puedo cambiar manualmente. El valor predeterminado era mejor cuando uno hackeado, por lo que debe ir a 5V para desactivar el énfasis. Este conmutador activa un transistor como en la sección mudo pero éste cambia la respuesta del filtro de salida girando/partes de la red de filtro - diseño de circuito análogo difícil.

Craquelador???

Creo que las grietas vienen de una deriva del reloj. El RPi impulsa los datos con su reloj de 44,1 kHz * 32 bits, la oversampler los procesos que con su propio reloj (también de 44.1 kHz * 32 (* 12 da 16.9 MHz)) ambos reloj deriva lejos hasta un bit de datos salta a su vecino poco escalado con eficacia por 2 que produce el pico de una sola muestra.

Solución 1 - extraer datos de la RPi con el excedente del reloj de samplers. Esto haría que el DAC y OS el reloj maestro. Implicaría cambiar el controlador del módulo (o usando otro)

Solución 2 - ser hacker hardware loco y construir un multiplicador de reloj. Esto podría multi el reloj de datos (44100 * 2 * 16 por segundo) por 6 o 12 para producir el reloj para el circuito de sobremuestreo. Esta voluntad de eliminar el segundo reloj y su voluntad de ser nada a la deriva, ya que todos los relojes se derivan de un reloj común.

Una forma de lograrlo podría ser el uso de una línea de retardo. Otro implica PLLs - nuevo para mí también. Pensamiento...