Paso 5: Construir un multiplicador de reloj 6 x

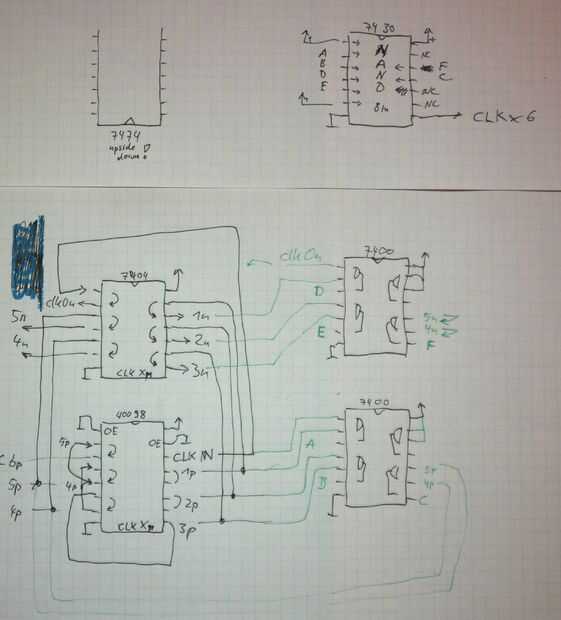

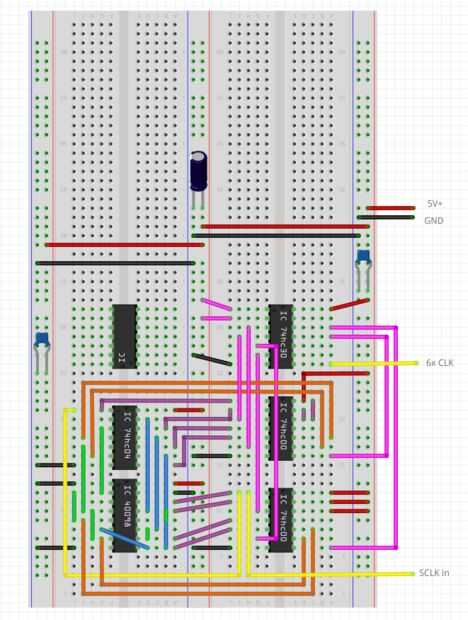

La cosa se llama "Reloj multiplicador con línea de retardo". Es algo simple. Retrasar la señal de reloj original por periodo de 1/6 y hacer un poco de lógica con estos resultados de señales retardadas en un nuevo reloj 6 veces más rápidamente que el original.

Problema: Encontrar una línea de retardo definidas.

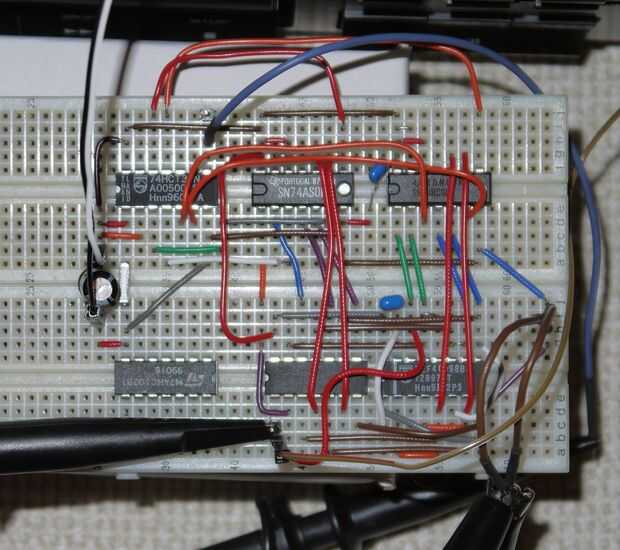

Solución: prueba y error!!! Encontré los inversores CMOS 40098 tener alrededor de unos 150 ns retardo de propagación. Esto es muy cerca de la deseada 118ns 708ns/6 (44100 muestras con 16 bits y 2 canales -> 44100 * 16 * 2 es 1,4112 MHz SCLK que es un ~ 708ns reloj de período)

Un poco más o menos retraso dará todavía la misma frecuencia no tan lisa, las subidas y bajadas tiene diferente longitud.

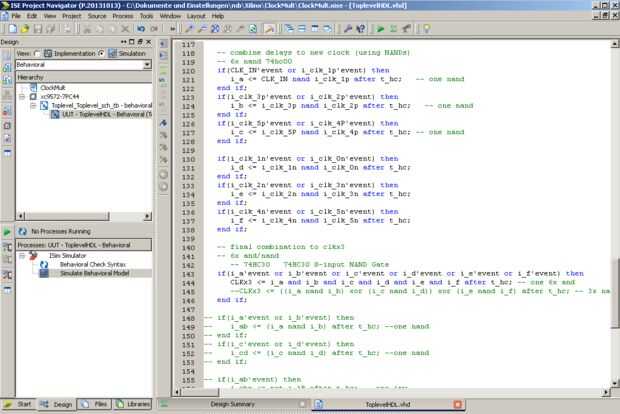

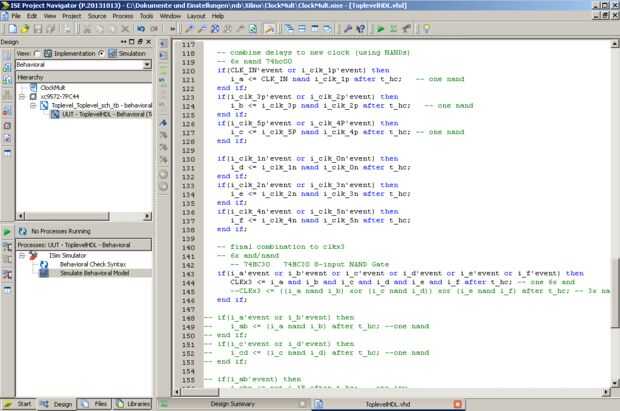

Simulación

De proyectos anteriores sé Xilinx ISE herramientas, que están libremente disponibles para hacer programación FPGA y CPLD. Puede hacer simulación lógica mediante esquema, entrada de diseño VHDL o Verilog. Esquema podría ser bueno para principiantes pero es muy doloroso cambiar las cosas en él. Un lenguaje de descripción de hardware es mucho más flexible, aunque por supuesto más para aprender.

De todos modos, la simulación es sólo para que mí para ver si la idea funciona y comprobar que la lógica haría el truco. Si está interesado, puede encontrar el proyecto de simulación que se adjunta, descomprimirlo y abrir el "ClockMult.xise" con ISE. Una vez que hecho hasta ahora se puede grabar en una CPLD, no, quieres diversión vintage! :)

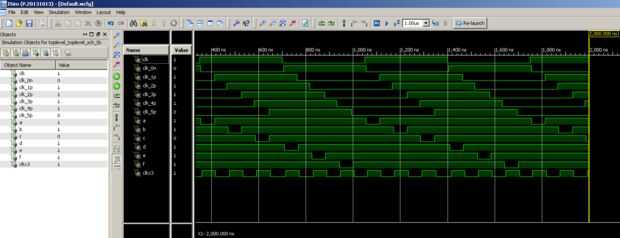

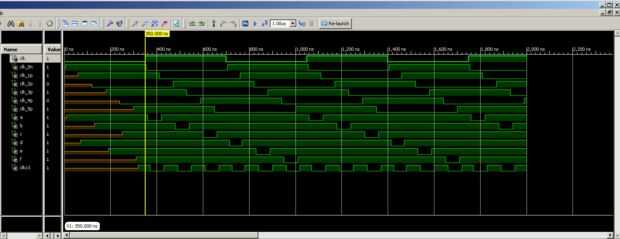

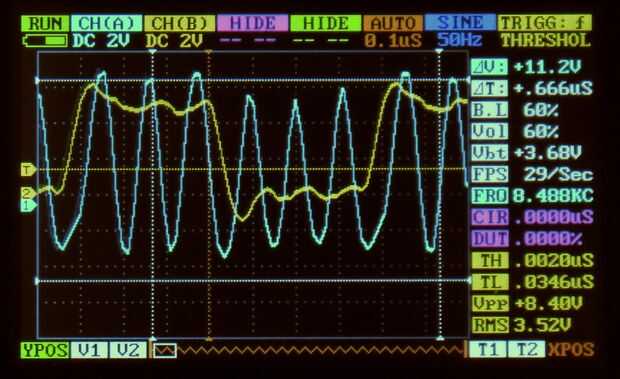

El resultado puede verse en las imágenes. El reloj va a la 5 40098 veces (6to inversor no utilizado), en cada salida puedes ver la anterior entrada invertida y retraso. las señales se llaman clk_Xp y clk_Xn para positivo y negativo (un poco irritante que aquí porque todas las salidas de la 40098 se llaman p aunque cambiar... Cada salida y el reloj original pase a través de un segundo Inversor (rápido) que es un 74hc04 para cada señal retardada está disponible como positivo (no invertida) y negative(inverted).

Después inversión escoger dos señales que pueden ser AND'ed para formar un solo pulso con la duración de 1/6 del reloj.

Los pulsos son luego OR'ed juntos dando el reloj 6 x final.

La y es realmente NAND 74hc00 ICs (eso y con la salida invertida) por hacer el pulso negativo. Para obtener el mismo resultado, estos debe ser AND'ed (N) en lugar de OR'ed. NAND o y no importa porque no me importa la polaridad de relojes final, o al menos yo puedo simplemente inviértala otra vez con el 74hc00 o 74hc04.

OK, esto realmente funciona, en teoría ;-)

Para hacer uso del nuevo reloj de 8,4672 MHz PCB de Kenwood debe cambiarse un poco. El SM5807 funciona con 16,9344 MHz, que es dos veces tanto como el 6xCLK pero la hoja de datos dice también funciona con el 8.4..MHz cuando el pin 3 (CKSL) está conectado a 'L' en vez de 'H'. Por supuesto la señal de reloj original debe extraerse de pernos de 1. Nuestro nuevo reloj bonito entonces se alimenta en este pin.

Vamos a salir el PCB y cambiar pin 3 de la SM5807 a la tierra y añadir a un pinheader para el reloj.

Desde el manual de servicio de DP3010 parece mejor quitar el cristal 16.9344 y agregue el jefe del perno en su lugar (el pin hacia el pin 5 de la 7402) entonces el reloj se invierte una vez más, no importa, hace simple modificación. Pin 2 y 3 de la SM5807 parecen inconexos, así que sólo agrego un puente desde el pin 3 a tierra. Debe hacerlo. Bastante simple.

enchufe, enchufe...

¿Y?

YYYYYYYYYYYYEEEEEEEEEESSSSSSSSSSSSS!

Obras, sin clics, enfríen.

Fue muy divertido :-)

¿No hay inconvenientes?

Bien la placa no es la más confiable tecnología, toque aquí y allá hace que todo se vuelven locos. Tal vez el CPLD en un simple soldado PCB no es una mala idea después de todo.