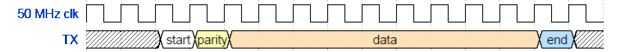

Paso 1: Planificación del transmisor

El transmisor requiere de tres cuadras.

- Reloj divisor - obtiene la velocidad correcta

- Registro de desplazamiento - empuja los datos de forma asincrónica a la computadora

- Estado de la máquina - controles el cambio de registro en el índice del divisor de reloj

Para ello utilizamos el diseño del "paquete" como se muestra en la imagen de arriba

El reloj de la tasa de baudios puede ser generado con:

divider = FPGA clock speed / desired baud rate

Para esto utilizamos 9600 baudios.

Un registro de desplazamiento se necesitará utilizar un búfer FIFO (primero en primera hacia fuera) para los datos junto con una máquina de estado con 2 Estados, ociosa y transmitir.