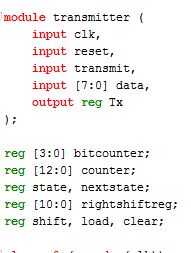

Paso 2: Crear el transmisor parte 1

El transmisor tiene las siguientes entradas y salidas:

- entrada clk (un reloj de 50 MHz)

- entrada de reset (reset alta activa la señal)

- transmisión de entrada (señal baja activa para saber el módulo para cargar nuevos datos)

- datos de entrada (valor de 8 bits para enviar transmitir la señal)

- salida Tx (el cable para transmitir en)

El

Primero implementamos el divisor del reloj como un contador. En 50 MHz, un reloj de 9600 baudios se puede generar con un contador que se restablece cada 5207 ciclos del reloj. El bloque de actualización de estado con palanca de cambios en este aspecto:

always @ (posedge(clk))begin if (reset) begin state <= 0; counter <= 0; bitcounter <= 0; end else begin counter <= counter + 1; if (counter >= 5207) //baud of 9600 at 50MHz clk begin state <= nextstate; counter <= 0; if (load) rightshiftreg <= {1'b1, ^data, data, 1'b0}; if (clear) bitcounter <= 0; if (shift) begin rightshiftreg <= rightshiftreg >> 1; bitcounter <= bitcounter + 1; end end end end