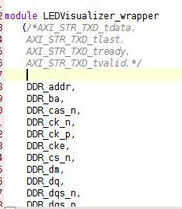

Paso 10: Edición de la envoltura de HDL

Ahora haga doble clic en "LEDVisualizer_wrapper" (la primera parte va a cambiar dependiendo de lo que se llamó su diseño). Tenemos que hacer algunos cambios aquí para incluir nuestro verilog personalizado en el diseño. Y como nota al margen, normalmente quieres hacer IP personalizado para ello. No tengo aquí porque cuando traté de hacer eso es algo de un dolor.

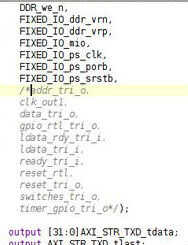

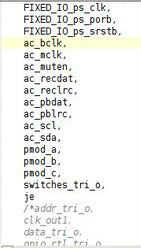

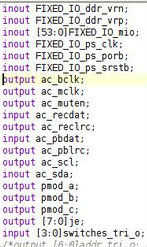

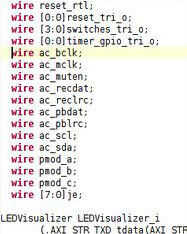

En primer lugar, comentar las cuatro señales a partir de "AXI" en la parte superior de la sección "module". Desplácese hasta la parte inferior de la sección de módulo y comente todo después de "FIXED_IO_ps_srstb". Entonces necesitamos agregar algunas señales en la sección de entrada y salida en el inicio. Mira las fotos arriba para ver cuáles. Ahora comentar las cuatro señales de entrada/salida "AXI". Ahora comente todas las señales de entrada/salida después de "FIXED_IO_ps_srstb". Añadir entonces las señales que se muestra en la foto de arriba. Ahora agregar los cables que se muestra en la foto de arriba a la sección de los cables. NO comente las señales de cable.

Ahora necesitamos saber el contenedor que queremos incorporar nuestro encargo Verilog en el sistema. Hacemos esto mediante la definición de instancias de nuestros módulos de Verilog en el contenedor. Seguir adelante y copiar las instancias del fsm, cuadro y AudioCodecSetup desde el archivo contenedor proporcionado y pégalos en tu propia (o sólo tienes que copiar el archivo contenedor entero de la que se ha proporcionado).

Por último, sólo tener en cuenta que si usted llama algo diferente entonces hice obtendrá errores al intentar generar el flujo de bits. Mantener un ojo hacia fuera para eso!

Después de guardar el archivo, observará que todos del módulo están ahora bajo los archivos de contenedor en el panel fuentes.