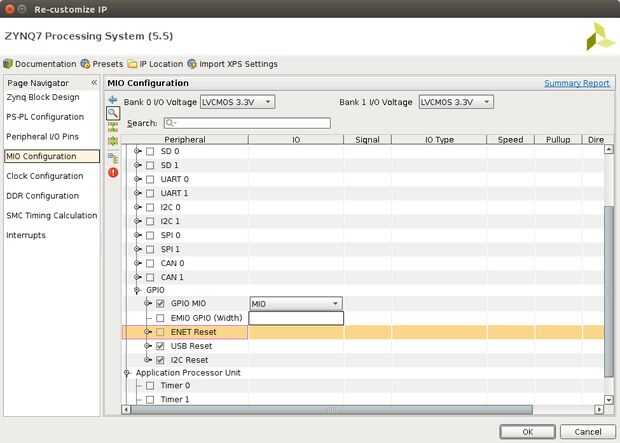

Paso 2: Configuración del bloque de Zynq

Ahora haga clic en la pestaña de "Configuración del MIO" en el lado izquierdo de la pantalla. Expandir "Periféricos de E/S". Compruebe ambos "SD 0", "ENET 0", y "UART 1". Luego expandir "GPIO" dentro de eso. Marque la casilla "GPIO MIO". Algunas otras cajas serán comprobado, así que está bien. Luego expandir "Unidad de procesador de aplicación" y comprobar "tiempo 0" y "Vigilante".

Haga clic en la pestaña de "Configuración del reloj" en el lado izquierdo de la pantalla. Ampliar el "PL tela relojes". Asegúrese de que está seleccionado "FCLK_CLK0" y que su valor es de 100 MHz.

Ahora haga clic en la pestaña de "Interrupciones" en el lado izquierdo de la pantalla. Haga clic en el cuadro "Interrumpe la tela". Luego expandir "PL-PS" y marque la casilla "IRQ_F2P [15:0]". Esto se utilizará más adelante en el proyecto para generar interrupciones para el procesador de la FPGA. Siga adelante y haga clic en "Aceptar" en la parte inferior derecha de la ventana.